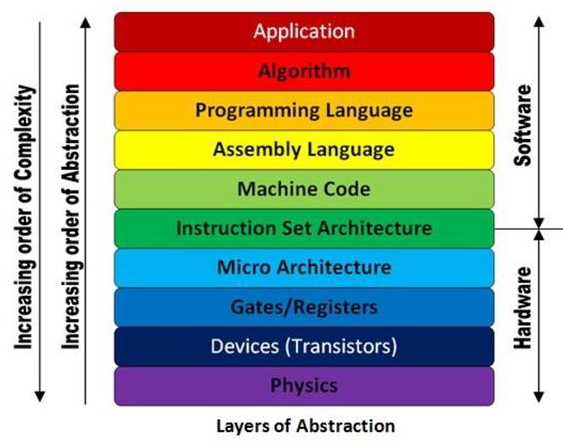

Обобщенное устройство электронных вычислительных систем описывается через выделение иерархии из десяти уровней абстракции. Такой вариантов описания показан на рисунке 0-0. Уровни иерархии объединяются в две крупные части: software (программная) и hardware (аппаратная). В данной статье мы приближаемся к физическому уровню и рассматриваем устройство аппаратных уровней абстракции.

Рисунок 0-0. Иерархия уровней абстракции вычислительной системы

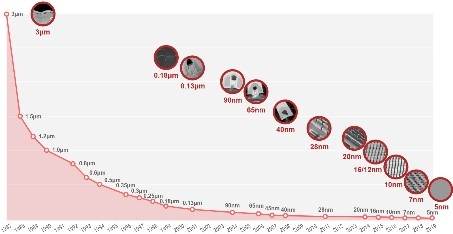

На рисунке 1-1 представлен временной график уменьшения разрешающей способности технологии производства.

Рисунок 1-1. Эволюция технологического процесса

Рисунок 1-1. Эволюция технологического процесса

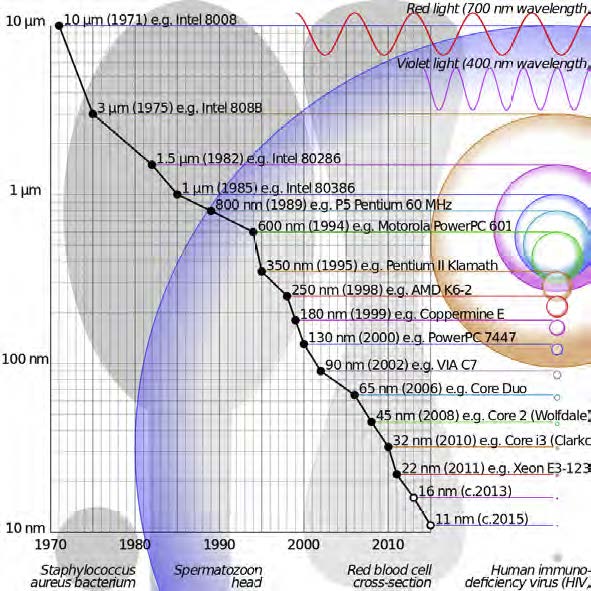

На рисунке 1-2 представлен график эволюции размеров транзисторов по сравнению с микробиологическими формами жизни – бактерии, головки сперматозоида, эритроцита, вируса иммунодефицита человека. Сверху рисунка для сравнения показаны соразмерно длины волн границ видимого человеку диапазона электромагнитного излучения – красный и фиолетовый.

Рисунок 1-2. Эволюция минимального размера транзистора

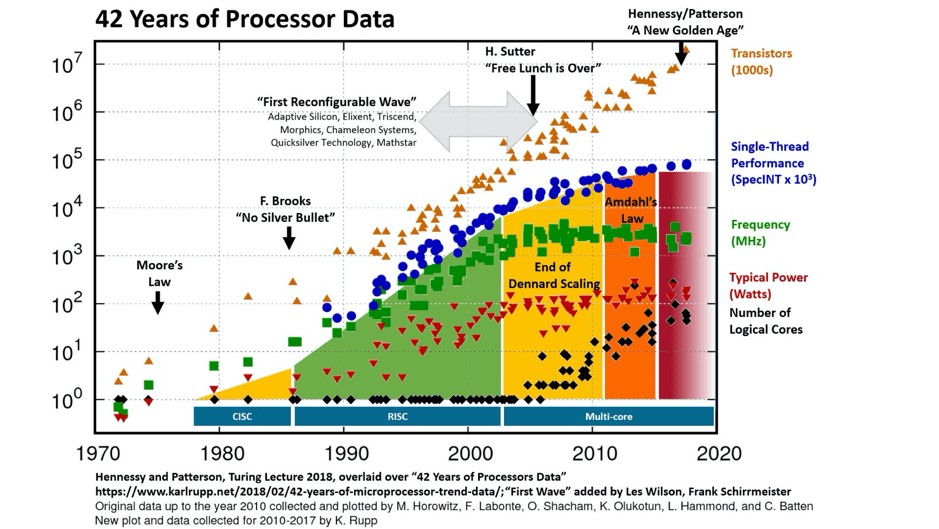

На рисунке 1-3 представлен график эволюции характеристик центрального процессора. Можно наблюдать выделяющееся увеличение количества транзисторов, тренд на замедление роста однопоточной производительности и типичной мощности потребления, достижение предела в максимальной рабочей частоте и переход на применение многоядерной архитектуры.

Рисунок 1-3. Эволюция характеристик процессоров

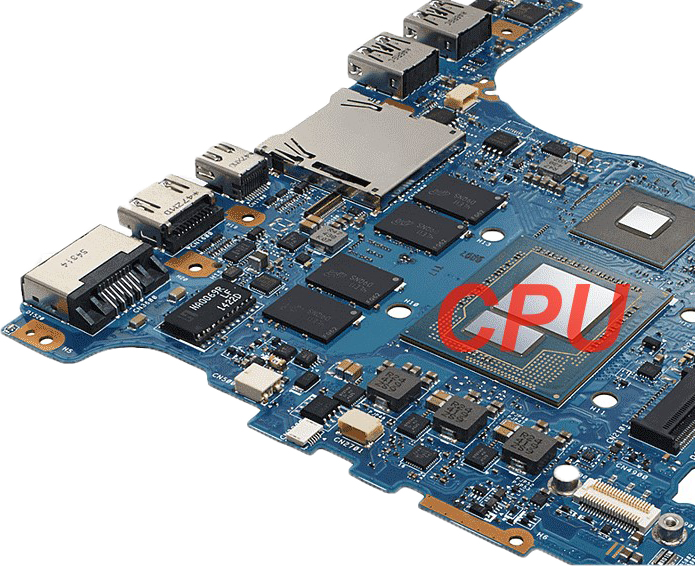

Работа цифровых устройств, окружающих нас, обеспечивается применением интегральных микросхем широкого спектра функциональности (см. рисунок 2-1).

Рисунок 2-1. Микросхемы. Внешний вид

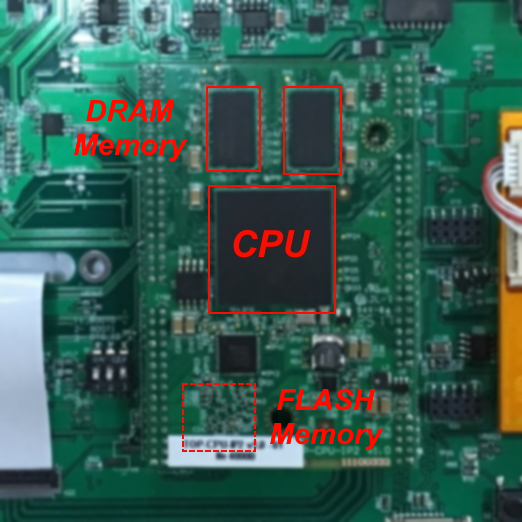

На рисунках 2-1 и 2-2 показаны примеры внутреннего размещения электронных блоков в ноутбуке и переговорном устройстве, а также выделены области размещения центрального процессора CPU, который является аппаратным мозгом большинства электронных изделий.

Рисунок 2-2. Ноутбук. Внутреннее устройство

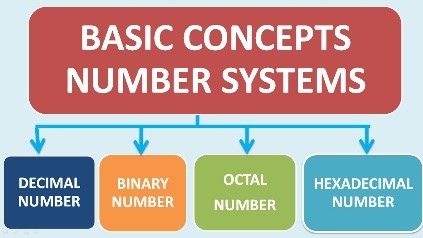

Выбор двоичной системы счисления для реализации физического базиса электронной техники был сделан еще в середине прошлого века (см. рисунок 3-1). Главная причина – упрощение электрической схемы, физической структуры логических элементов, памяти и снижение количества используемых транзисторов. Основная наша десятичная система имеет вполне логическое объяснение совпадения с количеством пальцев на руках.

Рисунок 3-1. Основные системы счисления

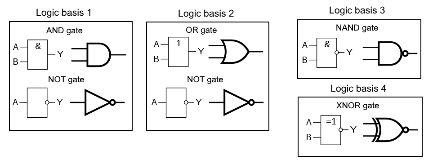

В те времена начала развития полупроводниковых вычислительных машин среди всех логических операций выделили четыре базиса из набора логических элементов, через каждый из которых в отдельности можно выразить любые другие логические операции – в том числе сложение и умножение (см. рисунок 3-2).

Рисунок 3-2. Полные логические базисы

Рисунок 3-2. Полные логические базисы

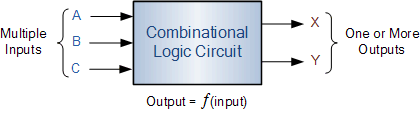

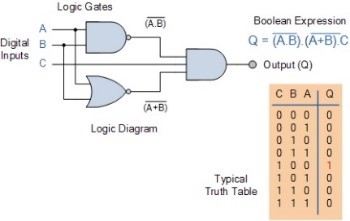

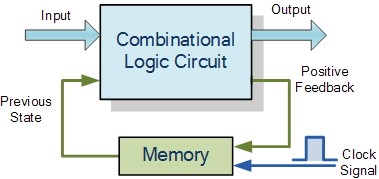

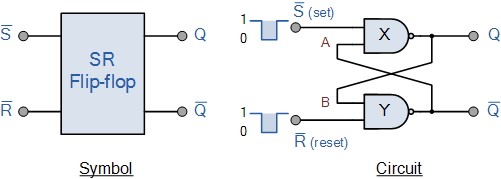

Все функциональные блоки цифровых микросхем состоят из логики двух типов: комбинаторная (см. рисунок 3-3) и последовательная, которая содержит ячейки памяти (см. рисунок 3-4). На рисунке 3-5 представлен простейший элемент памяти на логических элементах с обратной связью.

Рисунок 3-3. Комбинаторная логика

Рисунок 3-3. Комбинаторная логика

Рисунок 3-4. Последовательная логика

Рисунок 3-4. Последовательная логика

Рисунок 3-5. Простейший элемент памяти на логических элементах

Рисунок 3-5. Простейший элемент памяти на логических элементах

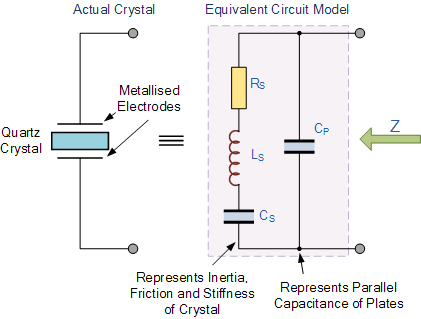

К функциям электронного сердца изделия можно отнести кварцевые генераторы на основе пьезо-кристалла (см. рисунок 3-6).

Рисунок 3-6. Источник тактирования кварцевый

Рисунок 3-6. Источник тактирования кварцевый

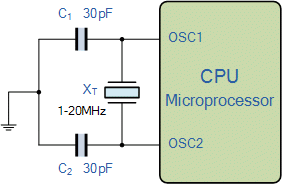

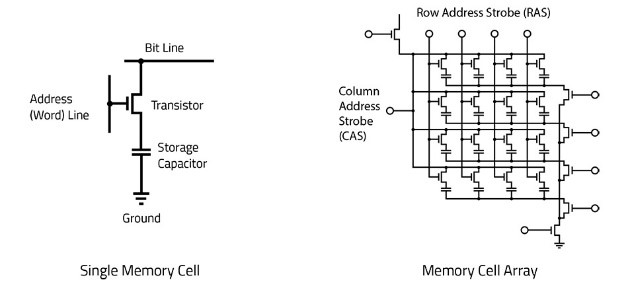

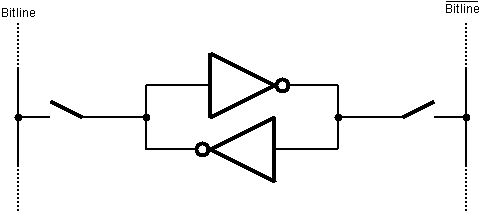

Все распространенные типы памяти хранят двоичное состояние «0» или «1». Энергозависимая память подразделяется на динамическую DRAM и статическую SRAM память. Ячейка динамической памяти (см. рисунок 4-1) состоит из микроразмерных конденсаторов, которые необходимо перезаряжать время от времени, иначе при отключении питания информация теряется. Кстати по такому же принципу работает и наш мозг. Ячейка статической памяти (см. рисунок 4-2) использует положительную обратную связь и способна поддерживать свое состояние без регенерации.

Рисунок 4-1. DRAM ячейка (cell)

Рисунок 4-1. DRAM ячейка (cell)

Рисунок 4-2. SRAM ячейка (cell)

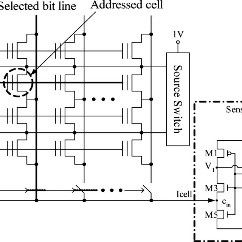

Для длительного хранения в выключенном состоянии используется в основном энергонезависимая полупроводниковая FLASH-память (см. рисунок 4-3). Ее ячейки состоят из транзисторов внутри которых сформированы конденсаторные нано-емкости с управляемым состоянием и возможностью изолироваться от внешней среды при отключении питания. Это гарантирует длительное сохранение заряда.

Рисунок 4-3 FLASH ячейка (cell)

Рисунок 4-3 FLASH ячейка (cell)

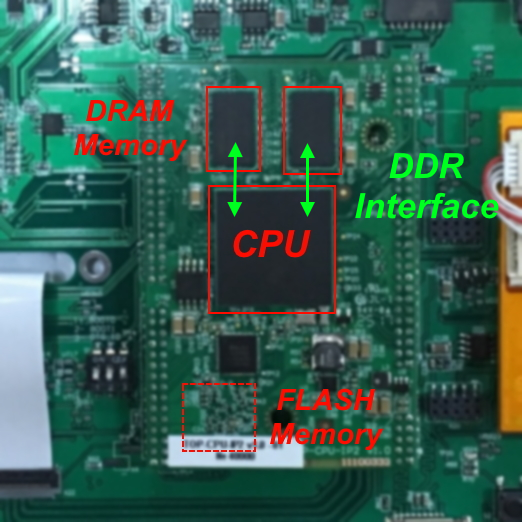

На рисунке 4-4 отмечены микросхемы динамической памяти на конденсаторах на процессорном модуле.

Рисунок 4-4. Микросхемы памяти на CPU модуле

Рисунок 4-4. Микросхемы памяти на CPU модуле

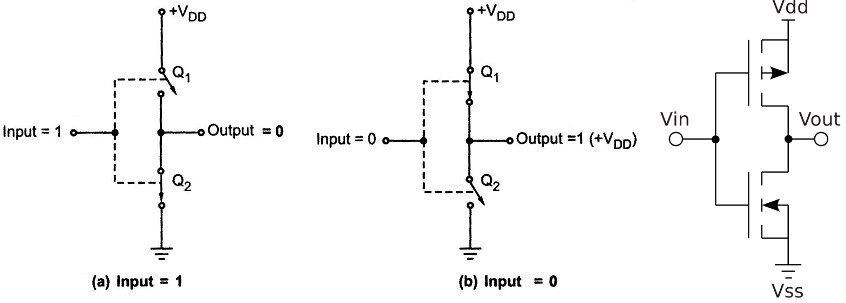

Самый простейший логические элемент – инвертор (см. рисунок 5-1). Его логическая и транзисторная схемы, и принцип работы представлены на рисунке 5-2. По сути он подключает выход элемента к питания «Vdd» или к опорному потенциалу/земле «Vss» схемы, в зависимости от двоичного состояния на входе. Повторитель (или буфер) это уже два последовательно включенных инвертора.

Рисунок 5-1. Условно-графическое отображение инвертора

Рисунок 5-1. Условно-графическое отображение инвертора

Рисунок 5-2. Транзисторная схема инвертора

Рисунок 5-2. Транзисторная схема инвертора

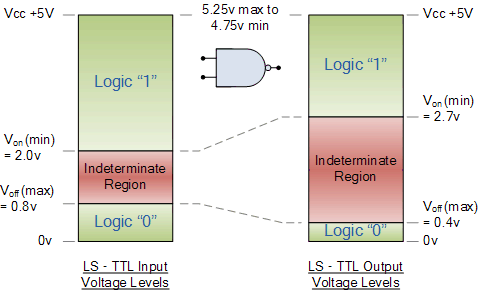

Типовые уровни напряжения двоичных состояний для входов и выход логического элемента при электропитании напряжением +5 V показаны на рисунке 5-3.

Рисунок 5-3. Уровни напряжения двоичных состояния вход/выходов

для электропитания с напряжением +5 V.

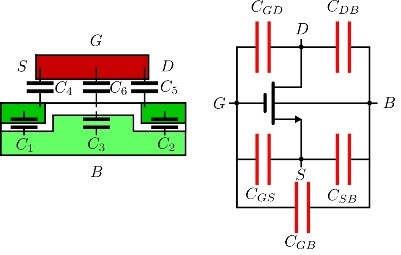

Основная причина тенденций на снижение напряжения питания вычислительного ядра – уменьшения минимального размера полупроводникового транзистора до уровня нано-метров. От габаритов полупроводниковых структур прямо прорционально зависит формируемая паразитная емкость (см. рисунок 5-4), значения пробивного напряжения и токов утечек. Общее потребление вычислительного сердца устройства складывается из динамической и статической составляющих (см. рисунок 5-5). Первая определяется переразрядом паразитных емкостей, импульсных утечек тока и зависит от частоты переключений, вторая – задается током утечки при сохранении текущего состояния. Таким образом вся используемая для вычислений энергия преобразуется в тепловую форму. Традиционно напряжения питания ядра современных процессоров, работающих на частотах свыше 500 МГц может варьироваться в диапазоне +0,7 – 1,5 В.

Рисунок 5-4. Паразитные емкости структуры транзистора

Рисунок 5-4. Паразитные емкости структуры транзистора

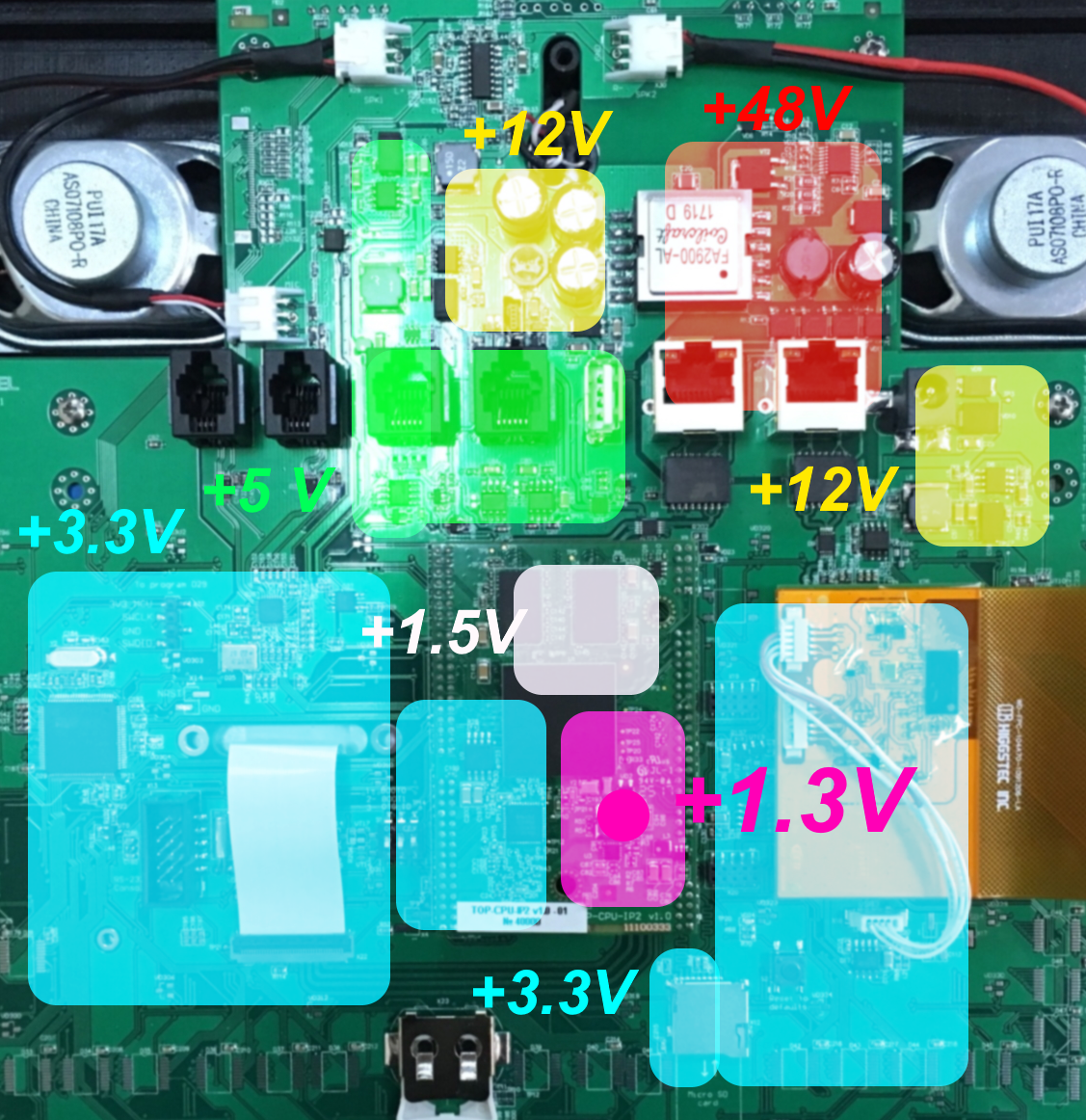

На рисунке 5-6 цветными зонами выделены области расположения напряжений электропитания от +48 V до +1.3 V на примере материнской платы переговорного устройства. Для обеспечения оптимума между вычислительной и электрической мощностью цифрового устройства напряжение питания высокочастотных вычислительных ядер снижается до минимально допустимого значения. На печатной плате рисунка 5-6 можно выделить тенденцию постепенного снижения напряжения по мере приближения к вычислительному мозгу системы.

Рисунок 5-6. Материнская плата переговорного устройства

Рисунок 5-6. Материнская плата переговорного устройства

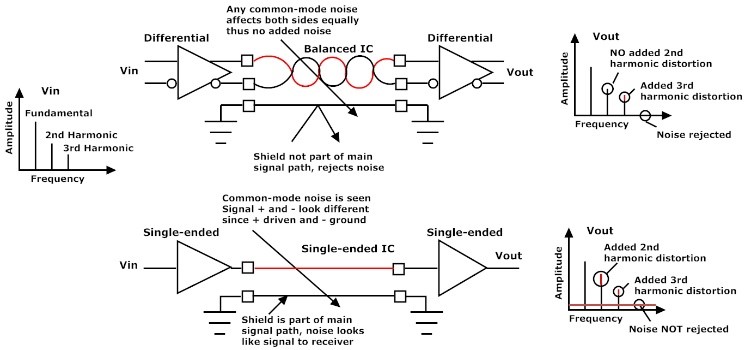

Для передачи информации в электрическом виде между микросхемами выделяют две основных способа: однополярный (single-ended) и дифференциальный (differential). На рисунке 6-1 представлены схемы обоих способов и отображена разница в частотном спектре выходного сигнала. В однополярной схеме для передачи сигнала используется один проводник и слой с общим потенциалом для возвратных токов передаваемого сигнала. В дифференциальной схеме используется два провода для передачи пары сигналов, где один представляет инвертированное состояние другого. При такой схеме передачи информации прямой и возвратный сигнальный ток сосредоточен именно в паре связанных сигналов и не используются линии опорного потенциала – это существенно улучшает помехозащищенность интерфейса, ослабляя электрическую связь между линиями передачи, расположенными рядом.

Рисунок 6-1. Однополярный сигнал, сигнал DDR

Рисунок 6-1. Однополярный сигнал, сигнал DDR

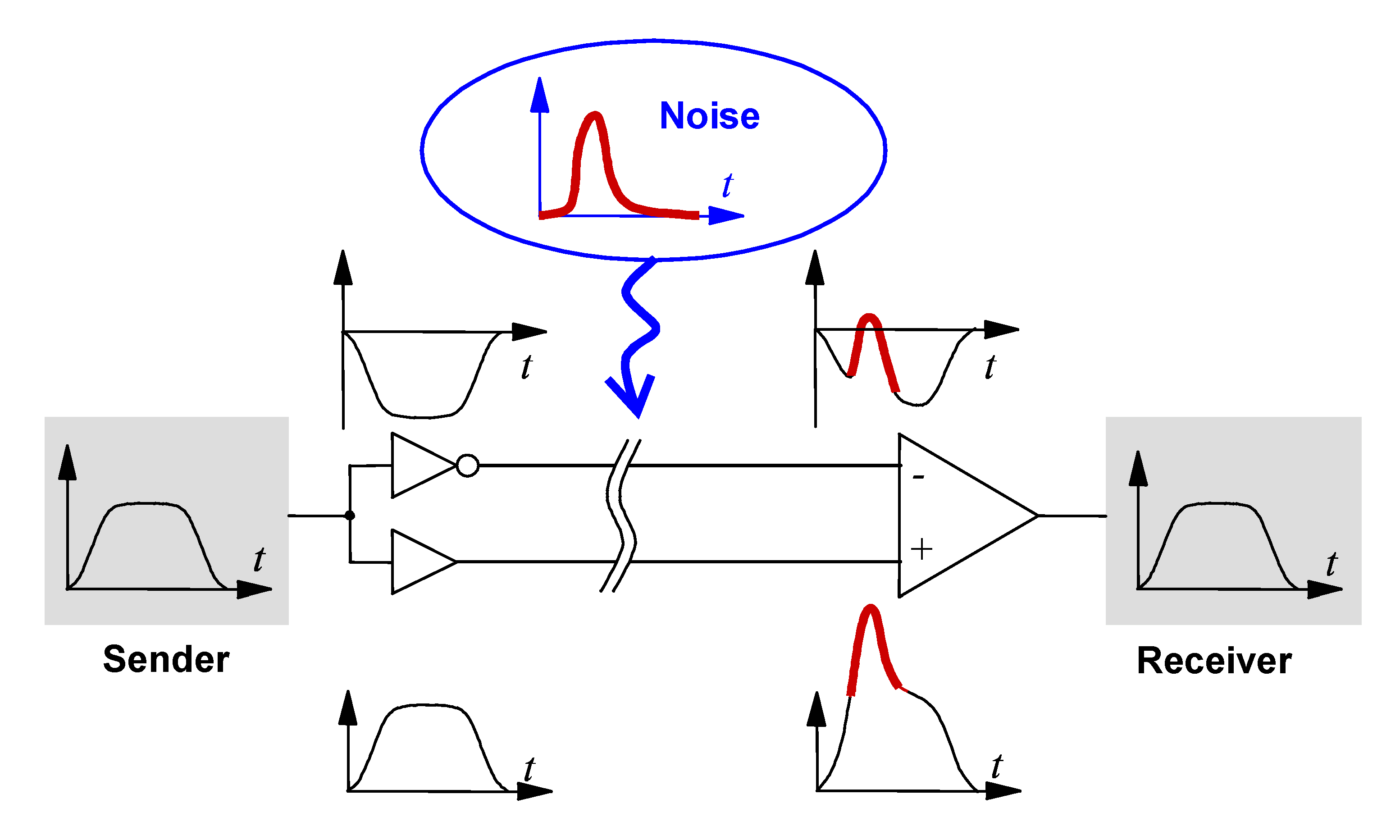

Рисунок 6-2 отображает помехоустойчивое преимущество дифференциального (симметричного) способа передачи данных по отношению к однополярному (несимметричному). При использовании симметричного подключения между приемником и передатчиком, например, кабель типа «витая пара» — помеха, одинаково наведенная на оба провода дифференциальной пары вычтется сама из себя на разностной схеме входа приемника. Большинство современных проводных высокочастотных интерфейсов передачи данных между микросхемами и отдельными устройствами используют дифференциальную схему включения, которая при небольшом усложнении выигрывает у однополярной по максимальной рабочей частоте, степени помехоустойчивости и уровню паразитных электромагнитных излучений. Например: USB, SATA, HDMI, DVI, PCI-Express, Ethernet и другие.

Рисунок 6-2. Вычитание внешней помехи в дифференциальном приемники

Рисунок 6-2. Вычитание внешней помехи в дифференциальном приемники

Наиболее распространенный интерфейс подключения памяти к вычислительному ядру является DDR SDRAM. Для основных сигналов линий адреса и данных используется однополярные сигналы, но со значительно уменьшенной разницей в уровнях напряжений логической единицы «1» и нуля «0». Это вызвано необходимостью снижения перекрестных взаимных помех при распараллеленной передачи данных на высокой частоте в ограниченной размером области печатной платы. На рисунке 6-3 показан процессорный CPU модуль с отмеченными областями размещения высокочастотного интерфейса памяти DDR.

Рисунок 6-3. DDR интерфейс на модуле CPU

Рисунок 6-3. DDR интерфейс на модуле CPU

Для обеспечения обмена данными между отдельными стационарными и мобильными вычислительными устройствами используется огромное разнообразие систем передачи данных. Среди проводных и беспроводных интерфейсов передачи данных наибольшее распространение получили системы на основе широкополосных технологий. Последнее подразумевает разбиение общих входящего и исходящего битового потоков на множество отдельных битовых под-потоков, для каждого из которых выделяется отдельная полоса частот… Раскрытие широкополосных методов преобразования информации, а также знакомство с волшебством квадратурной модуляции предстоит в следующей статье.

Автор статьи:

Семенчик Олег

Старший инженер-схемотехник